## Wide Input Range CC/CV Synchronous Buck Regulator

Unauthorized Photocopy and Duplication Prohibited

#### **Features**

- ♦ 5V ~ 32V Supply Voltage Range

- ♦ 36V Input Voltage Surge

- ♦ 32V Input Over Voltage Protection

- ♦ 2% Voltage Reference Accuracy

- ♦ 5% Constant Current Accuracy

- External Optional Current Limit Mode

- ◆ Programmable Frequency (60KHz ~ 1MHz)

- Built in Adjustable Line-Compensation

- ◆ Hiccup Short Circuit Protection

- ◆ Duty Cycle Range (0~100%)

- ♦ Internal Soft Start 3ms

- ◆ CC/CV Mode Control

- SOP-8L Package

## **Applications**

- Car Chargers

- ◆ DC/DC Converters with Current Limit

Portable Charger Devices

## **General Description**

The SP1233FL is a synchronous buck Regulator with output current up to 3.4A.It is designed to allow for operating a wide supply voltage range from 5V to 32V. The internal compensation requires a minimum number of readily available standard external components.

The SP1233FL operates in the CC(Constant output Current) mode or CV(Constant output Voltage) mode, and the OCP current value is set by current sensing power resisters or setting non power resisters.

The SP1233FL is suitable for the DC/DC switching power applications when requested the current limit function. The devices are available in SOP-8L package and require very few external devices for operation.

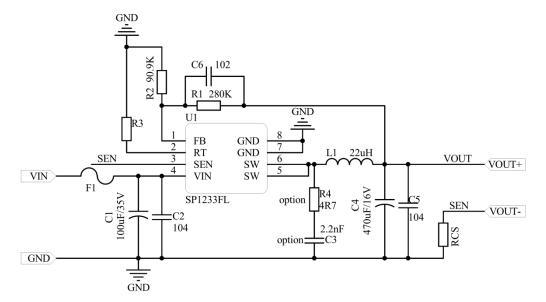

## **Typical Application Circuit**

Figure 1 Typical Application of SP1233FL(High-accuracy Current Limit)

#### Note1:

1.RCS=120mV/I<sub>limit.</sub>,RCS is Power Resistors.

2.RT=24000K/f<sub>osc</sub>; Float frequency is 120KHz.

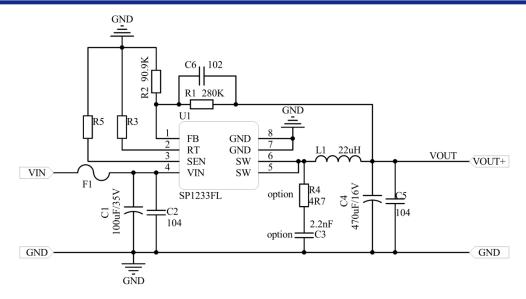

# Wide Input Range CC/CV Synchronous Buck Regulator

Figure2 Typical Application of SP1233FL(Low-cost Current Limit)

#### Note2:

- $1.R5>25K\Omega.R5$  is Non Power Resistors.

- 2. lout =3.1A recommend R5=82K;

lout =2.4A recommend R5=66.5K.

3.RT=24000K/fosc; Float frequency is 120KHz.

Si-power

Wide Input Range CC/CV Synchronous Buck Regulator

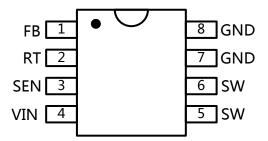

## **Pin Function Description**

Figure 3 Pin Configuration

| Pin No. | Pin Name | Function Description                                                                                                                                                                                                                        |

|---------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | FB       | Feedback Pin. The voltage at this pin is regulated to 1.2V. Connect to the resistor divider between output and GND to set the output voltage.                                                                                               |

| 2       | RT       | Frequency Setting Pin .Float frequency is 120KHz.                                                                                                                                                                                           |

| 3       | SEN      | The Current Sense or Setting Input Pin. When the SEN Pin is connected Power resistors to load, the current is set by $120 \text{mV/R}_{\text{sen}}$ . When the SEN Pin is connected Non Power resistor to GND, the current is set by note2. |

| 4       | VIN      | Power Supply Input. Bypass this pin with a 1uF ceramic capacitor to GND, placed as close to the IC as possible.                                                                                                                             |

| 5.6     | SW       | Power Switching Output to External Inductor.                                                                                                                                                                                                |

| 7.8     | GND      | Ground. Connect this pin to a large PCB copper area for best heat dissipation, Return FB, to this GND and connect this GND to power GND at a single point for best noise immunity.                                                          |

# **Ordering and Marking Information**

| Part Number | Package Description | Top Marking | Package Form |

|-------------|---------------------|-------------|--------------|

| SP1233      | SOP-8L              | SP1233FL    | SOP-8L       |

# Si-power Wide Input Range CC/CV Synchronous Buck Regulator

## **Absolute Maximum Ratings**

| Characteristics                             | Symbol         | Rating                                             | Units |

|---------------------------------------------|----------------|----------------------------------------------------|-------|

| Supply Input Voltage                        |                | -0.3 to +36                                        | V     |

| SW to GND                                   |                | -1 to +V <sub>IN</sub> +1                          | V     |

| FB,RT, SEN to GND                           |                | 0.3 to +7                                          | V     |

| ESD HBM(Human Body Mode)                    |                | ±2K                                                | V     |

| ESD MM(Machine Mode)                        |                | ±200                                               | V     |

| Power Dissipation, PD @T <sub>A</sub> =25°C | P <sub>D</sub> | (T <sub>J</sub> -T <sub>A</sub> )/ θ <sub>JA</sub> | W     |

| Thermal Resistance from Junction to case    | $\theta_{JC}$  | 40                                                 | °C/W  |

| Thermal Resistance from Junction to ambient | $\theta_{JA}$  | 160                                                | °C/W  |

#### Note3:

1. Stresses listed as the above "Absolute Maximum Ratings" may cause permanent damage to the device.

These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may remain possibility to affect device reliability.

- 2. Devices are ESD sensitive. Handling precaution recommended.

- 3. θ <sub>JA</sub> is measured in the natural convection at T <sub>A</sub>= 25°C on a high effective thermal conductivity test board of JEDEC51-7 thermal measurement standard.

## **Recommended Operating Conditions**

| Symbol | Description                             | Value       | Units |

|--------|-----------------------------------------|-------------|-------|

| TST    | Storage Temperature Range               | -65 to +150 | °C    |

| TJ     | Junction Temperature                    | -40 to +150 | °C    |

| TOP    | Operating Temperature                   | -40 to +85  | °C    |

|        | Lead Temperature Range(Soldering 10sec) | 260         | °C    |

Si-power

Wide Input Range CC/CV Synchronous Buck Regulator

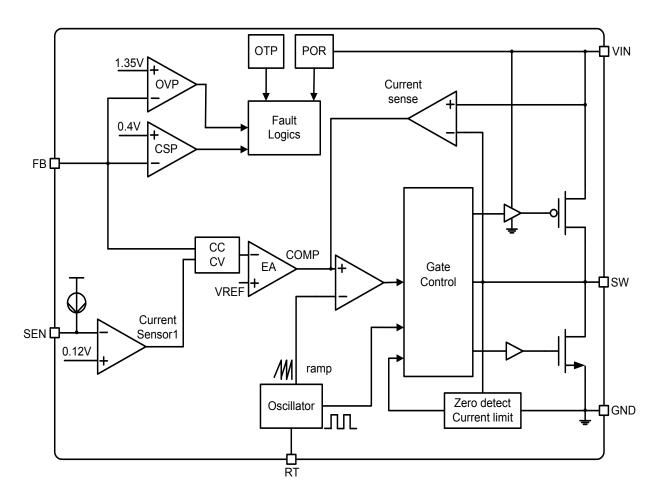

## **Block Diagram**

Figure 4 Block diagram of SP1233FL

### **Electrical Characteristics**

$V_{CC}$  = 12V,  $T_A$  = +25°C, unless otherwise specified

| Characteristics                      | Symbol             | Test Conditions                   | Min | Тур  | Max  | Units |  |

|--------------------------------------|--------------------|-----------------------------------|-----|------|------|-------|--|

| Supply Voltage Range V <sub>IN</sub> | V <sub>cc</sub>    |                                   | 5   | -    | 32   | V     |  |

| Quiescent Current                    | I <sub>cc</sub>    | Vin=12V,Vout=5V,no load           | -   | 0.6  | -    | mA    |  |

| Quiescent Current                    | Icc                | Vin=24V,Vout=5V,no load           | -   | 0.3  | -    | mA    |  |

| Power-On-Reset                       |                    |                                   |     |      |      |       |  |

| VCC POR Threshold                    | $V_{CCRTH}$        | Vcc Rising.                       |     | 4.5  |      | V     |  |

| VCC FOR THESHOLD                     | $V_{CCFTH}$        | Vcc Falling.                      |     | 4.3  |      | v     |  |

| Oscillator                           |                    |                                   |     |      |      |       |  |

| Normal PWM Frequency                 | Fosc               | I <sub>OUT</sub> =200 mA,RT float | 60  | 120  | 1000 | KHz   |  |

| Duty Cycle Range                     | Duty               |                                   | 0   | -    | 100  | %     |  |

| Reference                            |                    |                                   |     |      |      |       |  |

| Reference Voltage                    | $V_{REF}$          |                                   | -   | 1.2  | -    | V     |  |

| Reference Voltage Tolerance          |                    |                                   | -2  | -    | +2   | %     |  |

| Line compensation Current            | I <sub>FB</sub>    | lout=1A                           | -   | 0.44 | -    | uA    |  |

| Current Sense Amplifier (Power Resi  | stors)             |                                   |     |      |      |       |  |

| SEN Voltage                          | $V_{SEN}$          |                                   | 114 | 120  | 126  | mV    |  |

| Current Set (Non Power Resistors)    |                    |                                   |     |      |      |       |  |

| Rsen=82K                             | I <sub>limit</sub> | Vin=12V,Vout=5V                   |     | 3.8  |      | Α     |  |

| Rsen=66.5K                           | I <sub>limit</sub> | Vin=12V,Vout=5V                   |     | 2.8  |      | Α     |  |

| Protection                           |                    |                                   |     |      |      |       |  |

| Over Temperature Shutdown            |                    |                                   | -   | 160  | -    | °C    |  |

| Over Temperature Hysteresis          |                    |                                   | -   | 40   | -    | °C    |  |

| Soft Start                           |                    |                                   |     |      |      |       |  |

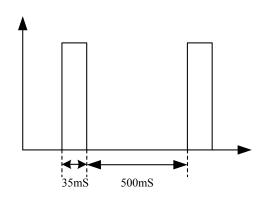

| Soft Start Time                      | T <sub>SS</sub>    |                                   | -   | 3    | -    | ms    |  |

| Recycle Time                         |                    |                                   | -   | 500  | -    | ms    |  |

| Output Short Circuit Protect Section |                    |                                   |     |      |      |       |  |

| Short Circuit Fold Back Voltage      | $V_{SCP}$          |                                   | -   | 0.4  | -    | V     |  |

| MOSFET                               |                    |                                   |     |      |      |       |  |

| Up PMOS On Resestance                | Rdson              |                                   |     | 42   |      | mΩ    |  |

| Down NMOS On Resestance              | Rdson              |                                   |     | 23   |      | mΩ    |  |

# i-power Wide Input Range CC/CV Synchronous Buck Regulator

## **Functional Description**

#### **CV/CC** mode control

The SP1233FL provides CC/CV function. The Constant output Current control Mode and Constant output Voltage control Mode.

#### **Over Current Protection**

The SP1233FL provides over current protection. A drop voltage on the current sensing resister is over the OCP value, the OCP function will shut down the controller.

#### **Soft Start**

The SP1233FL has internal soft start function to control rise rate of the output voltage and limits the large inrush current at start up. The typical soft start interval is about 3mS.

#### **Power on Reset**

A power-on reset circuit monitors the input voltage. When the input voltage exceeds 4.5V, the converter will start operation. Once input voltage falls below 4.3V, the controller will shut down.

#### **Over Temperature Protection**

The SP1233FL provides over temperature protection. The OTP will shut down the converter when junction temperature exceeds 160°C.Once temperature cools down by approximately 40°C, the converter will resume normal operation.

#### **Current Limit Protection**

The SP1233FL provides two kinds of current limit Mode. When the SEN Pin series Power Resistors to the load. The current limit set according to the following equation:

$$CurrentLimit(A) = \frac{120mV}{R_{SEN}}$$

When the SEN Pin series Non Power Resistors to GND. The current limit set according to the following:

| Rsen | 82K  | 66.5K |

|------|------|-------|

| lout | 3.1A | 2.4A  |

#### **Oscillator Frequency**

The SP1233FL oscillator frequency is set by a single external resistor connected between the RT pin and the GND pin. The resistor should be located very close to the device and connected directly to the pins of the IC (RT and GND). The oscillator frequency rises when the resistor RT falls. To determine the timing resistance for a given switching frequency, use the equation below:

$$f(KHz) = \frac{24000K}{R_{T}}$$

#### **Output Short-Circuit Protection**

The SP1233FL provides output short-circuit protection function. When  $V_{OUT}$  is short ( $V_{FB}$ <0.4V), the auto restart function can be started that restart the regulator cycle by cycle. The cycle time is set by internal counter.

Figure 5 short-circuit protection time

# Si-pwer Wide Input Range CC/CV Synchronous Buck Regulator

### APPLICATION INFORMATION

#### **Output Voltage Setting**

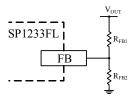

Figure 6 Output Voltage Setting

Figure 6 shows the connections for setting the output voltage. Select the proper ratio of the two feedback resistors R<sub>FB1</sub> and R<sub>FB2</sub> based on the output voltage. Typically, use  $R_{FB2}$ >10k $\Omega$  and determine  $R_{FB1}$  from the following equation:

$$R_{\text{FB1}} = R_{\text{FB2}} \left( \frac{V_{\text{OUT}}}{1.2} - 1 \right)$$

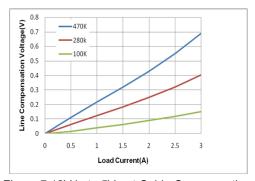

#### **Output Cable Resistance Compensation**

To compensate for resistive voltage drop across the charger's output cable, the SP1233FL integrates a simple, user-programmable cable voltage drop compensation using the impedance at the FB pin. R<sub>FB1</sub> is the high side resistor of voltage divider.

$$V_{\text{OUT}} = \left[ \left( 1 + \frac{R_{\text{FB1}}}{R_{\text{FR2}}} \right) \cdot 1.2 \right] + \left[ R_{\text{FB1}} \cdot \text{Iout} \cdot 0.44 \right]$$

Figure 7 12V in to 5V out Cable Compensation

#### **Inductor Selection**

The inductor maintains a continuous current to the output load. This inductor current has a ripple that is dependent on the inductance value:

Higher inductance reduces the peak-to-peak ripple

current. The tradeoff for high inductance value is the increase in inductor core size and series resistance, and the reduction in current handling capability. In general, select an inductance value L based on ripple current requirement:

$$L = \frac{V_{\text{OUT}} \times (V_{\text{IN}} - V_{\text{OUT}})}{V_{\text{IN}} f_{SW} I_{\text{OUTMAX}} K_{\text{RIPPLE}}}$$

Where  $V_{IN}$  is the input voltage,  $V_{OUT}$  is the output voltage,  $f_{SW}$  is the switching frequency,  $I_{OUTMAX}$  is the maximum output current, and K<sub>RIPPLE</sub> is the ripple factor. Typically, choose K<sub>RIPPLE</sub>=30% to correspond to the peak-to-peak ripple current being 30% of the maximum output current. With this inductor value, the peak inductor current is I<sub>OUT</sub> × (1+K<sub>RIPPLE</sub>/2). Make sure that this peak inductor current is less than the controller's current limit. Finally, select the inductor core size so that it does not saturate at the peak inductor current.

#### **Input Capacitor**

The input capacitor needs to be carefully selected to maintain sufficiently low ripple at the supply input of the converter. A low ESR capacitor is highly recommended. Since large current flows in and out of this capacitor during switching, its ESR also affects efficiency.

The input capacitance needs to be higher than 100µF. The best choice is the ceramic type, however, low ESR tantalum or electrolytic types may also be used provided that the RMS ripple current rating is higher than 50% of the output current. The input capacitor should be placed close to the VIN and GND pins of the IC, with the shortest traces possible. In the case of tantalum or electrolytic types, they can be further away if a small parallel 1µF ceramic capacitor is placed right next to the IC. Especially C2 capacitor should be placed as close as possible to the VIN pin.

#### **Output Capacitor**

The output capacitor also needs to have low ESR to keep low output voltage ripple. The output ripple voltage is:

$$V_{RIPPLE} = I_{OUT} K_{RIPPLE} R_{ESR} + \frac{V_{IN}}{28 \times f_{SW}^2 L C_{OUT}}$$

Where  $I_{\text{OUTMAX}}$  is the maximum output current,  $K_{\text{RIPPLE}}$  is

# Wide Input Range CC/CV Synchronous Buck Regulator

the ripple factor,  $R_{ESR}$  is the ESR of the output capacitor,  $f_{SW}$  is the switching frequency, L is the inductor value, and  $C_{OUT}$  is the output capacitance. In the case of ceramic output capacitors,  $R_{ESR}$  is very small and does not contribute to the ripple. Therefore, a lower capacitance value can be used for ceramic type. In the case of tantalum or electrolytic capacitors, the ripple is dominated by  $R_{ESR}$  multiplied by the ripple current. In that case, the output capacitor is chosen to have sufficiently low ESR. For ceramic output capacitor, typically choose a capacitance of about  $470\mu F$ . For tantalum or electrolytic capacitors, choose a capacitor with less than  $50m\Omega$  ESR.

#### **PCB Layout Recommendations**

- 1. PCB trance defined as SW node, which connects to the inductor, should be as short and wide as possible.

- 2. Inductance between the SW terminal and the output VOUT as far as possible with the ground wire to reduce the output side of the switch coupling.

- ALL sensitive analog traces such as SEN and FB should place away from high-voltage switching nodes SW nodes to avoid coupling.

- 4. Input bypass capacitor should be placed to the IN pin as close as possible.

- 5. Feedback resistor should be placed to the FB pin as close as possible.

- 6. Gather the ground terminals of the  $V_{\text{IN}}$  capacitor(s),  $V_{\text{OUT}}$  capacitor(s), and the source of the low-side MOSFETs as close as possible. Signal ground and power ground should be connected strongly together near the device.

- 7. The ground of input capacitance and output capacitance should be placed as close as possible.

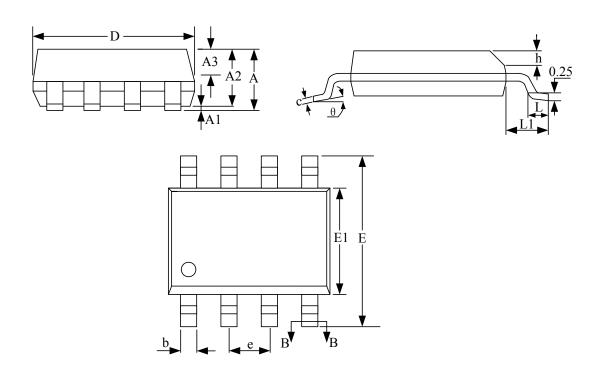

# **Package Information (Units:mm)**

| Cumbol | Dimensions in Millimeters |      |      |  |

|--------|---------------------------|------|------|--|

| Symbol | Min.                      | Nom. | Max. |  |

| А      | -                         | -    | 1.75 |  |

| A1     | 0.05                      | _    | 0.15 |  |

| A2     | 1.30                      | 1.40 | 1.50 |  |

| A3     | 0.60                      | 0.65 | 0.70 |  |

| D      | 4.70                      | 4.90 | 5.10 |  |

| Е      | 5.80                      | 6.00 | 6.20 |  |

| E1     | 3.70                      | 3.90 | 4.10 |  |

| е      | 1.27BSC                   |      |      |  |

| h      | 0.25                      | -    | 0.50 |  |

| L      | 0.50                      | -    | 0.80 |  |

| L1     | 1.05BSC                   |      |      |  |

| θ      | 0                         | -    | 8°   |  |

# **SP1233FL**

Si-pwer

Wide Input Range CC/CV Synchronous Buck Regulator

### **Restrictions on Product Use**

- Si-Power is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing Si-Power products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such Si-Power products could cause loss of human life, bodily injury or damage to property.

- In developing your designs, please ensure that Si-Power products are used within specified operating ranges as set forth in the most recent Si-Power products specifications.

- The information contained herein is subject to change without notice.